Bentley N. Scott and Gailon E. Brehm

Texas Instruments Incorporated

Central Research Laboratories

P.O. Box 225936, M/S 134

Dallas, Texas 75265

ABSTRACT

A GaAs Voltage Controlled Oscillator Circuit that tunes from 11.15 to 14.39 GHz and 16.0 to 18.74 GHz has been designed and fabricated. The 1.1 mm x 1.2 mm chip includes two varactors, a 300  $\mu$ m FET, bypass capacitors, tuning inductors and isolation resistors. Wideband circuit design techniques will be described. Varactor and circuit effects causing the non-continuous bandwidth will be discussed showing the capability of continuous 11 to 18 GHz tuning using a single GaAs chip.

Introduction

Major emphasis in the past 5 years in monolithic GaAs circuits has been in amplifier, mixer, T/R switch and phase shifter networks while oscillator development has continued to be hybrid oriented. The first microwave monolithic oscillator above L-band including both the power generating and tuning elements on a single chip was previously reported by the authors<sup>1</sup>. This circuit covered 8.8 to 10.0 GHz. The present work allowing two varactors to be implemented, one in the source and one in the gate circuits has given a tuning bandwidth covering 11.15 to 14.39 GHz and 16.0 to 18.74 GHz from a single chip. This circuit demonstrates the capability to cover X and Ku-bands continuously with one monolithic circuit. The design technique used and a description of the unique varactor are summarized with an explanation relating to the varactor Q which created the frequency gap between 14.39 and 16 GHz. The development work was done under NRL contract # N00173-79-C-0048 with funding by the Naval Air Systems Command.

Circuit Design

The negative impedances required to cause oscillations in a MESFET are a result of positive feedback. If the correct feedback reactance is added to a properly selected device configuration, oscillations can occur from very low frequencies to approximately  $f_{max}$  of the active device. After comparing the possible combinations both analytically and experimentally, the common gate configuration utilizing an inductive reactance between gate and ground as the regenerative feedback element was selected due to its inherent broadband negative resistances and ease of analysis. A varactor was placed in series with the inductor to tune the negative impedances across a wide bandwidth.

In order to make design trade-offs between the tuning circuit topologies and arrive at element values which would produce a wide bandwidth oscillator, several simplifying assumptions were required. Small signal S-parameters were used to characterize the FET and this data is then used to predict tuning bandwidths since oscillations build up from small signal conditions. Non-linear device behavior due to large signal operation of the device was assumed to be primarily a change in source-drain resistance which does not appreciably change the phase angle or magnitude of the negative impedances

appearing at the source with the drain appropriately loaded as in the case of this common gate design. A design technique that allowed representative bandwidth and element value predictions was developed that entails characterization of the device by S-parameter measurements, stability circle analysis, drain circuit definition, computer generation of composite S-parameters utilizing the selected drain circuit, and source circuit phase angle graphs which allow bandwidth and element value selection.

To perform this bandwidth analysis, first S-parameters are taken on a common source MESFET and a model is fit to the data. Using computer aided design programs the model is transformed to a common gate device with a series gate feedback inductor and stability circles are generated for varying values of this gate inductance. This family of circles defines the region of impedances that the drain must see to maintain negative source resistances as the gate feedback inductance is varied. A 15 ohm drain load will allow negative resistances to appear at 11 GHz with 1.2 nH net inductance in the gate and will also allow negative source resistances at 18 GHz if that net gate inductance is changed to .2 nH.

Maintaining negative impedances at the source makes it possible to terminate that port using an appropriate passive phase cancellation network that will allow oscillation to occur. Tuning is accomplished by varying the impedance (net inductive reactance) from gate to ground. The frequency at which negative impedance is seen at the source for a given gate inductance and drain matching network is the frequency at which free-running oscillations will occur (assuming an appropriate phase cancellation network is used to terminate the source). The relative magnitude of that negative impedance is an indication of the amount of tuning element (varactor) loss that can be tolerated and the amount of output power that can be obtained.

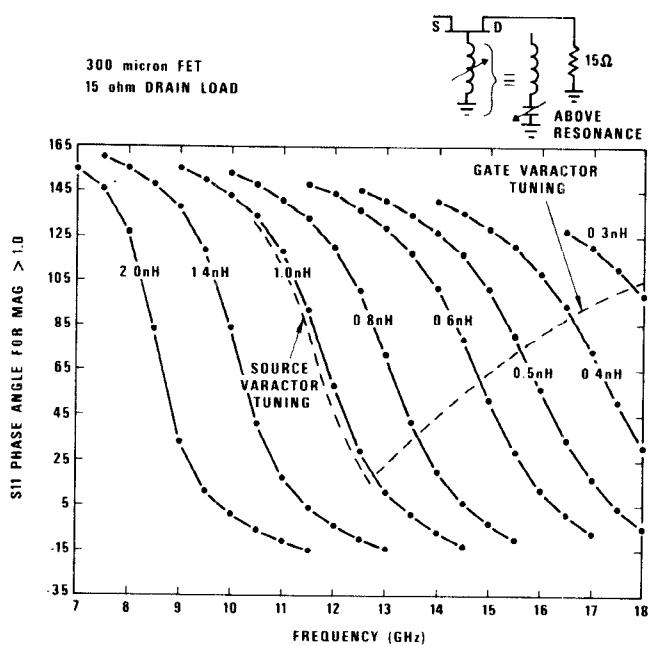

The family of curves generated using the above analysis is given in Figure 1. The abscissa is the phase angle of the source reflection coefficient (when it is greater than unity) with the drain loaded into a 15 to 50 ohm two-section transformer. From these data it was determined that a capacitive termination is required in the source network to cancel the imaginary part of the FET source impedance. The circuit then oscillates at that frequency where the source phase angle is cancelled and negative impedance is seen at the source. The bandwidth may be determined by

calculation of the terminating network's phase angle slope; the intersection of this slope and the varying gate inductance family (given by the net gate inductance value as the series varactor capacitance changes) gives the tuning bandwidth.

Figure 1. FET Source Reflection Coefficient Phase Angle vs. Frequency

Several hybrid oscillator circuits were built using this analytical approach. Results showed that selection of varactor values to achieve a particular bandwidth was possible. The frequency of oscillation was also predictable from use of this method for other circuit element value selection.

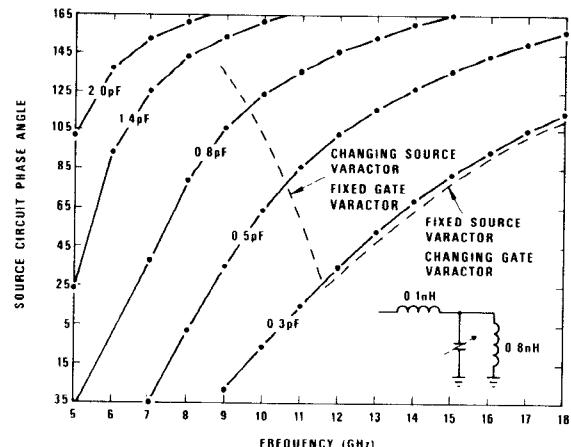

Oscillator circuits utilizing one varactor in the gate and terminated at the other two ports as described will give maximum tuning bandwidths of 4 GHz at X-band.<sup>2,3</sup> The tuning curves were used to study improvements in the source network which would increase tuning bandwidth. A varactor was added to the source network so that the phase angle could be tuned radically vs. frequency, thus improving the obtainable VCO bandwidth by more than 2.5 GHz.

Figure 2 shows phase vs. frequency data for the source network shown in the figure. As the varactor is tuned, the phase changes rapidly. If Figure 1 is considered to exemplify the FET phase angle requirements for oscillation then at 10.5 GHz with 1.0 nH in the gate, a phase angle of approximately -160° is required at the source circuit. As the source varactor (gate varactor value held constant) is tuned the source would follow the dotted line on Figure 2 since the oscillator would ride the 1.0 nH line given in Figure 1. At a source varactor value equal to 0.3 pF the frequency of the oscillation would be 14 GHz. If the gate varactor is now tuned (source varactor held constant while the gate varactor is tuned) frequency of oscillation will follow the source phase curve given by the 0.3 pF line in Figure 2. This source and gate tuning path is given by the dotted line in Figure 1 which shows

Figure 2. Source Circuit Phase Angle vs. Frequency

the source tuning the oscillator from 11 GHz to 14 GHz (with a source varactor swing of 1 to 0.3 pF) and the gate varactor tuning the oscillator from 14 GHz to 18 GHz (with a gate varactor swing of 1 pF to 0.13 pF). This example simply illustrates the basic tuning mechanisms and does not include all circuit parameter considerations required for proper analysis.

This varactor analysis which was developed at Texas Instruments has allowed TI to establish state-of-the-art tuning bandwidths for hybrid varactor tuned VCOs.<sup>4</sup> This technique allows a practical estimation of varactor swing and the circuit element values required for a given bandwidth.

Recently, efforts have been made to incorporate the FET, varactors, and capacitors on one piece of GaAs, thus reducing the present 1/4" x 1/4" oscillator circuit at X-band to .060" x .045". This reduced the number of bond wires and assembly steps required by a factor of five to ten times.

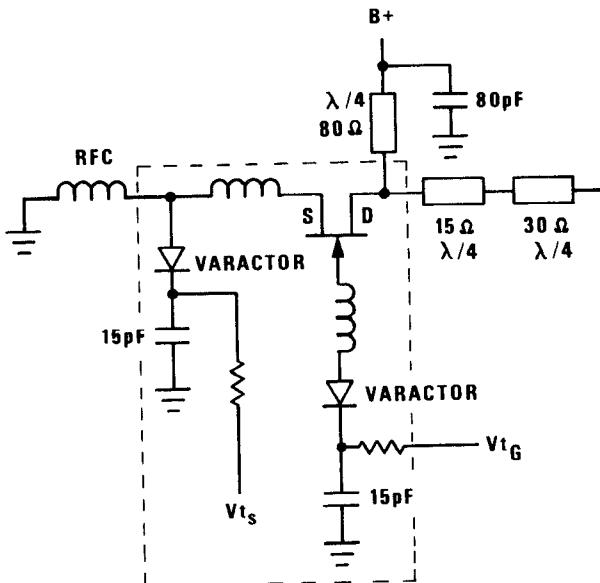

A circuit to obtain oscillations in X- and Ku-band was generated for monolithic implementation with the schematic given in Figure 3. The 15 to 50 ohm transformer was not placed on the mask for the GaAs chip in order to maximize the number of oscillator circuits obtained from each slice. Isolation resistors to reduce the chance of low frequency oscillations and to serve as current limiting resistors if the varactor diodes were accidentally forward biased were included on the chip.

#### Monolithic Varactor Diode

Conventional varactor diodes, particularly those with large tuning ratios (hyperabrupt diodes) require highly conductive substrate material and relatively thick epitaxial layers ( $> 1 \mu\text{m}$ ). These materials requirements are not compatible with those for GaAs FET-based monolithic microwave integrated circuits (MMICs) which require a thin ( $< 0.5 \mu\text{m}$ ), uniformly-doped active layer on a semi-insulating substrate. To integrate the conventional hyperabrupt diode on a semi-insulating substrate requires a very complicated selective epitaxial deposition. The materials required to fabricate the diode discussed here are the same as or very similar to those for the FET, so this device type will be extremely important in monolithic voltage controlled oscillators.

Figure 3. Monolithic VCO Schematic

Van Tuyl<sup>5</sup> has reported the use of a GaAs varactor diode in an MMIC which is similar in design and materials requirements to that discussed here. This device does not, however, provide the same wide-band capacitance tuning characteristics. This wide tuning range ( $C/C_0 > 10$ ) is essential for many microwave applications.

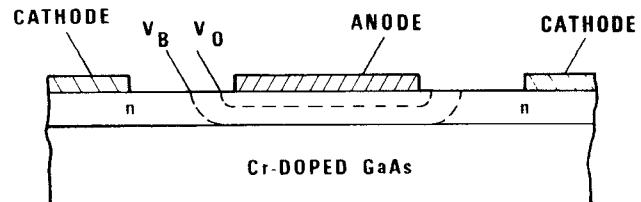

The device discussed here is an interdigitated Schottky-barrier diode and was reported on by the authors previously.<sup>6</sup> The key feature of the diode is that an arbitrarily high capacitance ratio is achieved by the change in the effective junction area as the depletion layer punches through on the semi-insulating substrate. A simple, uniformly doped n-layer on a Cr-doped or other semi-insulating GaAs substrate can be used. The layer thickness and/or the amount of anode recess is chosen to allow punch-through before breakdown. It consists of one or more Schottky-barrier anode fingers spaced between ohmic cathode regions. An n-type GaAs layer is defined by mesa etching and other means so that it is only under the active area. The bond pads (or interconnects to other parts of a monolithic circuit) are located on the semi-insulating substrate for minimum parasitic capacitance and conductance.

The key feature of the device is illustrated in Figure 4. The doping-thickness product of the n-layer under the anode is selected so that punch-through to the substrate occurs prior to breakdown. A rapid drop in capacitance occurs at punch-through because the effective area of the diode is reduced to that of the depletion layer sidewalls alone. The fractional drop in capacitance is related to the ratio of the anode length (direction parallel to current flow) to the layer thickness. The series resistance is related to the anode length and anode-cathode spacing.

The region beneath the anode prior to punch-through can be regarded as a distributed RC network. On that basis the equivalent terminal impedance can be calculated. The equivalent resistance,  $R_e$  and capacitance  $C_e$  are given by

$$R_e = 1/2 \sqrt{\frac{R_o}{2\omega C_0}} \frac{(\sinh \theta - \sin \theta)}{(\cosh \theta - \cos \theta)} + 1/2 R_s \quad (1)$$

Figure 4. Cross-section of Monolithic Varactor

$$\frac{1}{\omega C_e} = 1/2 \sqrt{\frac{R_o}{2\omega C_0}} \frac{(\sinh \theta + \sin \theta)}{(\cosh \theta - \cos \theta)} , \quad (2)$$

where  $\theta = L \sqrt{1/2\omega R_o C_0}$ ,  $R_s$  is the parasitic series resistance to the cathode on each side, and  $R_o$  and  $C_0$  are the resistance and capacitance per unit length under the anode. These equations do not include the sidewall capacitance, which were added in separately for biases near punchthrough.

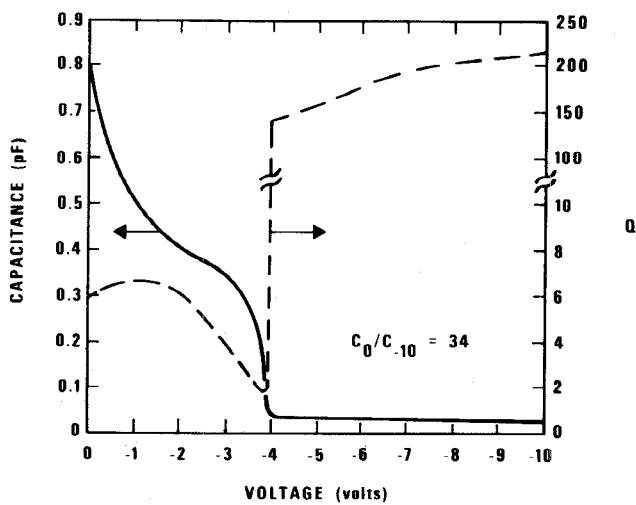

Using (1) and (2), the C-V characteristic, the series resistance and  $Q (= \frac{1}{\omega R_e C_e})$  at 10 GHz have been calculated for several appropriate diode designs. Figure 5 shows the C-V characteristics and  $Q$  for a  $6 \mu\text{m} \times 100 \mu\text{m}$  anode device. In this case the  $Q$  is 6 at zero bias and drops below 2 before punch through at approximately 3.8 volts. It is this sharp reduction in  $Q$  and a high surface leakage path on this slice of monolithic oscillators that caused the drop out in the center of the frequency band.

#### Experimental Results

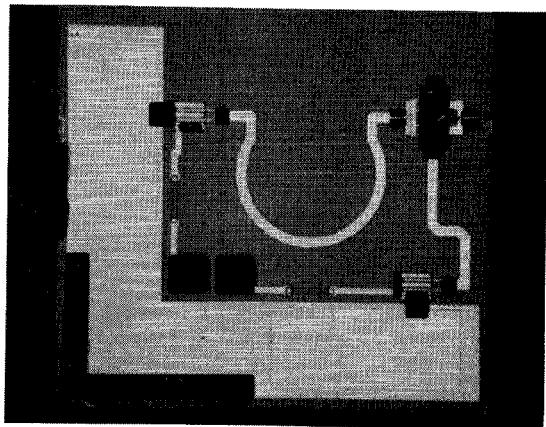

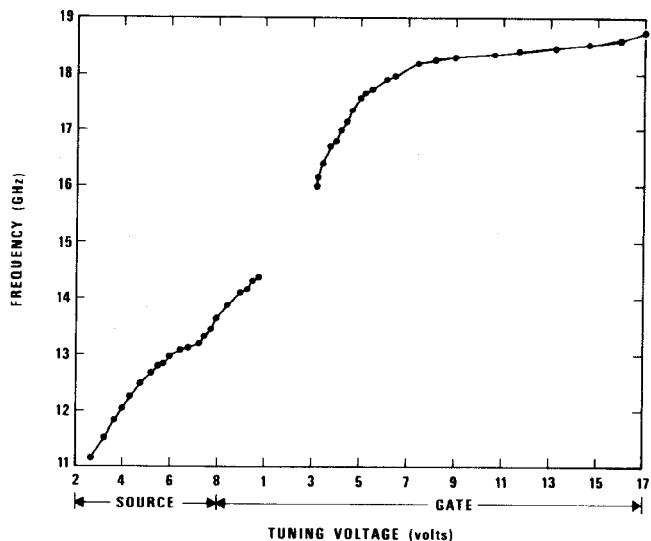

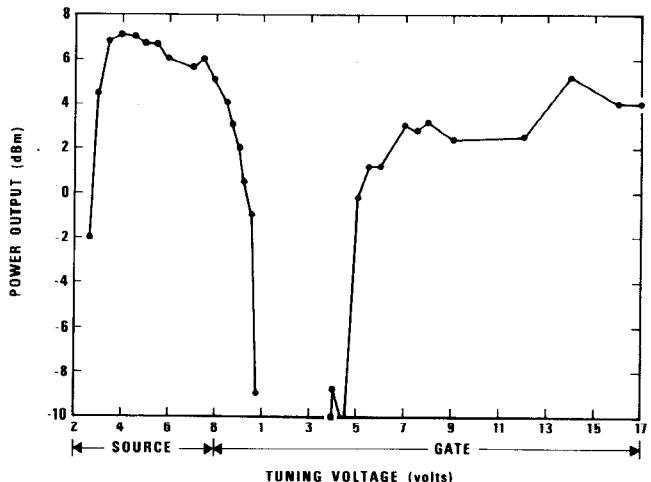

The varactor diodes, a  $300 \mu\text{m}$ , FET, and the associated circuitry discussed earlier were implemented on a single GaAs  $1.1 \text{ mm} \times 1.2 \text{ mm}$  chip as shown in Figure 6. The varactor diodes were designed for a  $1.0 \text{ pF}$  starting value and capacitance a ratio greater than 15:1. Figures 7 and 8 show the frequency and power respectively vs. tuning voltage of an oscillator as first the varactor in the source was tuned from 0 to 9 V, and then the varactor in the gate was tuned 0 to 17 volts. The actual voltage across the varactor was less in each case due to the voltage drop across the  $2 \text{ K ohm}$  resistor as the varactor became leaky. The oscillator tuned smoothly from 11.15 to 14.39 GHz where the oscillations ceased due to the low  $Q$  and excessive surface leakage across the diode. As the tuning voltage was increased on the gate to 3.2 volts the oscillation began once again at 16.0 GHz and continued tuning to 18.74 GHz.

#### Conclusion

A design technique has been developed that allows oscillator bandwidth to be predicted and tradeoffs to be performed between circuit configurations and varactor ratio.

Monolithic voltage tuned oscillators have been built on a 1.1 mm x 1.2 mm chip which included the 300  $\mu$ m FET, two varactors, and all of the associated circuit elements except the 15 to 50 ohm output matching transformer. These circuits exhibited a tuning performance of 11.15 to 14.39 GHz and 16.0 to 18.74 GHz. This performance demonstrates the feasibility of covering octave bandwidths continuously using monolithic technologies. Assembly problems, size, and repeatability of present hybrid VCO's should be vastly improved once this technology matures.

#### References

1. B.N. Scott, G.E. Brehm, and F.H. Doerbeck, "X-Band GaAs Monolithic Voltage Controlled Oscillators," ISSCC-82 Digest pp. 138-139.

2. H.Q. Tserng, H.M. Macksey, and V. Sokolov, "Performance of GaAs MESFET Oscillators in the Frequency 8-25 GHz," Electron. Lett. 13, 85 (1977).

3. H.Q. Tserng and H.M. Macksey, "Wide-Band Varactor-Tuned GaAs MESFET Oscillators at X- and Ku-Bands," 1977 International Microwave Symposium, Digest of Technical Papers, pp. 267-269.

4. B.N. Scott, G.E. Brehm, D.J. Seymour, and F.H. Doerbeck, "Octave-Band Varactor-Tuned GaAs FET Oscillator," ISSCC-81 Digest pp. 138.

5. R. Van Tuyl, "A Monolithic GaAs FET of Signal Generation Chip," ISSCC-80 Digest, pp. 118.

6. G.E. Brehm, B.N. Scott, D.J. Seymour, W.R. Frensley, W.N. Duncan, and F.H. Doerbeck, 1981 Cornell Microwave Conference Digest, p.

Figure 5. Theoretical CV Characteristic and Q for Recessed-Anode Varactor (6  $\mu$ m x 100  $\mu$ m Anode)

Figure 6. Photograph of Monolithic VCO

Figure 7. VCO Tuning Curve

Figure 8. VCO Output Power